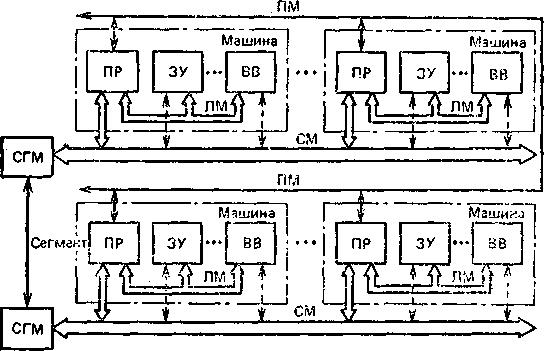

Общая архитектура ММС на базе интерфейсной системы содер-жит см рис. несколько сегментов, каждый из которых включает одну или несколько машин, имеющих в своем составе одноплатную.

микроЭВМ и платы, расширяющие ее возможности н подсоединяе-мые посредством локальной магистрали (ЛМ). Несколько машин, входящих в состав одного сегмента, связываются между собой по системной магистрали (СМ), выполненной в виде объединительной печатной платы. Отдельные сегменты соединяются друг с другом последовательной магистралью (ПМ) или через сегментатор (СГМ). Система состоит из набора модулей, каждый из которых, как правило, является абонентом СМ, а некоторые могут выходить на ПМ. Модули памяти могут быть абонентами ЛМ или СМ. Двухпор-товые модули памяти являются абонентами и ЛМ, и СМ.

Каждый сегмент имеет некоторые общесистемные средства (ге-нератор тактовых синхроимпульсов, аппаратуру арбитража и преры-вания, диагностические средства и т. п.), которые могут находиться в отдельных модулях либо рассредотачиваться по различным моду-лям.

Основной магистралью ММС, реализующей мультипроцессорную работу и объединяющей большинство модулей сегмента, является СМ. Самой быстродействующей магистралью, используемой обычно для расширения памяти процессоров, является ЛМ. Как правило, ЛМ имеет уменьшенное адресное пространство, меньшую нагрузочную способность по сравнению с СМ и может обслуживать один или два задатчика. Работа этих магистралей основывается на принципе <задатчик-исполнитель>. Несколько задатчиков используют магистрали с разделением времени в соответствии с заданным алгоритмом ар-битража.

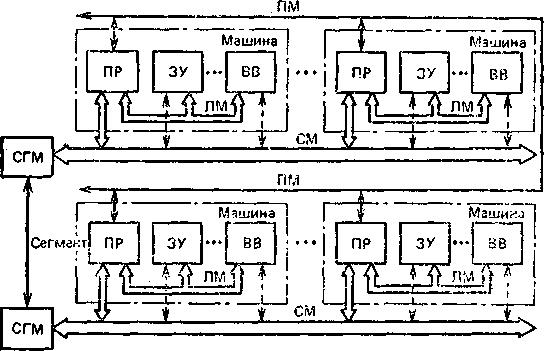

В табл. приведен состав магистралей новых зарубежных ин-терфейсов ММС, наиболее существенных для отечественных ММС аналогичного назначения.

В со-ставе Futurebus (P-896) регламентируются две магистрали: парал-лельная (Р) и последовательная (S). Магистраль ввода-вывода (ВВ) и ЛМ считаются входящими в систему пользователя и ограничения на них не накладываются.

В составе Fastbus (Фастбас) имеются СМ и кабельная магист-раль, образующие сегмент. В системе предусматривается использова-ние главной ЭВМ, которая через интерфейс процессора связывается с интерфейсами сегмента, соединяющими сегменты между собой с по-мощью кабеля. На каждом сегменте может быть несколько задатчи-ков или исполнителей.

Главным ограничением при построении ВС и СОД любой кон-фигурации является максимально допустимая протяженность маги-страли при заданной пропускной способности. Максимальная длина СМ обычно равна 50 см (число объединяемых модулей до 20), дли-на ЛМ-8... 12 см (число объединяемых модулей до 6), длина ПМ (кабельная линия с последовательной передачей данных) - до 10 м.

Интерфейсы ММС и СОД характеризуются рядом особенностей, отличающих их от интерфейсов ЭВМ и СОД первого поколения:

локализация потоков информации, обусловленная главным обра-зом специализацией отдельных машин или процессоров на отдельные виды работы (в этих условиях они информационно слабо связаны друг с другом, что позволяет эффективно локализовать потоки ин-формации и соответственно оптимизировать пропускные способности отдельных шин); уменьшение избыточности потока адресной информации за счет оптимизации местных шин для передачи команд и использования не-мультиплексированных шин адреса и данных, а также системных шин в качестве коммуникационных путей с преимущественно пакет-ным способом передачи по мультиплексируемым шинам адреса и дан-ных;

независимость магистрали от типа используемых микропроцес-соров (МП) и процессоров, позволяющая наращивать производи-тельность систем путем добавления в последующем модулей на но-вых поколениях МП;

способы адресации и адресные пространства (географический и логический способы, несколько адресных пространств и два вида доступа - индивидуальный и широковещательный);

механизм передачи межпроцессорных сообщений, обеспечиваю-щий быстродействующую аппаратную передачу блоков информации из одного процессора в другой.

Для реализации основных управляющих функций в современных интерфейсах, как правило, используется децентрализованное управ-ление, хотя в некоторых из рассматриваемых магистралей содержатся отдельные элементы централизованного управления (арбитраж, уп-равление инициализацией и прерываниями). В И-41 и MBI, напри-мер, все функции управления распределены между модулями и на магистрали отсутствует специальный централизованный модуль уп-равления. В MBII функции арбитража и управления прерываниями распределены между модулями, а функции инициализации и специа-лизированного управления выполняются центральным обслуживаю-щим модулем. В VME функции арбитража и управления прерыва-нием выполняет системный контроллер.

Наиболее общими характеристиками рассматриваемых интерфей-сов ММС являются: принципы управления (синхронный или асинхрон-ный протокол, централизованное или децентрализованное управле-ние); режимы передачи данных (одиночный, блочный, широковещательный); типы адресации (логическая, географическая, групповая, расширенная, псевдоадресация); степень и возможности мультипро-цессорное (одно-, двухпроцессорные, мультипроцессорные и сущест-венно мультипроцессорные системы); механизм передачи межпро-цессорных сообщений; разрядность н мультиплексирование адреса и данных (раздельные и совмещенные шины адреса и данных); на-личие аппаратного контроля на магистрали; конструктивное особен-ности (возможности использования печатных плат нескольких раз-меров, размеры плат и каркасов, конструкции объединительной пла-ты или кабеля и т. д.); степень проработки параметров системы, обеспечивающих более высокие по сравнению с ЭВМ эксплуатационные характеристики, простоту воспроизведения и совместимость изделий различных изготовителей; степень анонсирования отдельных эле-ментов промышленностью (несущих конструкций, соединителей, гото-вых модулей, а также специальных интерфейсных БИС).

При работе магистрали используются два основных типа прото-кола: синхронный и асинхронный. При синхронном протоколе (СП) все сигналы устанавливаются и проверяются относительно тактового синхроимпульса, а при асинхронном протоколе (АП) - в произволь-ное время. В большинстве современных интерфейсов применяется АП, и только в некоторых - СП. Последний обладает большей помехо-защищенностью, так как проверка управляющих сигналов произво-дится на фронте синхроимпульса, т. е. во <временном окне>, которое обычно составляет около 8 % общего времени работы. В остальное время- возможные помехи не оказывают влияния, тогда как при АП модули могут сработать от помехи почти в произвольный момент вре-мени. Кроме того, СП увеличивает надежность В связи с отсутствием на магистрали метапроцессов (в АП должна быть предусмотрена за-щита от метастабильных состояний, особенно при высокой частоте работы на магистрали); более прост в реализации, отладке и тестиро-вании (может быть использован логический анализатор). Однако СП менее гибок по сравнению с АП при использовании на магистрали модулей с различными скоростями работы. Недостатком СП является также наличие централизованного генератора тактовых синхросигна-лов.

Реализация блочного и широковещательного режимов передачи данных повышает быстродействие и расширяет функциональные воз-можности магистрали.

Мультиплексирование шин адреса и данных позволяет сущест-венно уменьшить число драйверов магистрали, сократить число кон-тактов соединителей модулей и линий на объединительной плате. Использование раздельных шин адреса и данных обеспечивает вы-сокую пропускную способность магистрали, особенно в режиме пе-рекрытия, когда во время текущего цикла передачи данных устанав-ливается адрес следующего цикла передачи.

Введение сигналов четности адреса и данных повышает надеж-ность работы информационного канала магистрали, но увеличивает затраты оборудования на формирование и проверку четности в мо-дулях. Передача сигналов управления в виде информационного кода с применением СП позволяет контролировать по четности и управля-ющие сигналы.

Использование географической адресации (наряду с логической) дает возможность программно настраивать режимы и диапазоны ад-ресов модулей, изменять конфигурацию системы и реконфигурировать ее при отказах.

Для реализации мультипроцессорной работы наряду с механиз-мом прерывания с последующим опросом источника прерывания или общей памяти в современных интерфейсах широко используется ме-ханизм передачи сообщений. Этот механизм позволяет передавать информацию из локальной памяти одного процессора в локальную память другого аппаратно с высокой скоростью (без программной взаимосинхронизации). При этом протокол передачи сообщений на-ряду с другими интерфейсными протоколами реализуется в интер-фейсных БИС.

Управляющие сигналы, как правило, передаются по магистрали в инверсном коде. Действующее значение сигнала имеет уровень лог. О (низкий уровень) транзисторно-транзисторной логики (ТТЛ), при отсутствии сигнала линия имеет уровень лог. 1 (высокий уровень).. Это позволяет объединять сигналы от разных модулей проводным . ИЛИ. При этом нарушение контактов соединителей или обрывы ли-ний (они более вероятны, чем ложное замыкание) приводят к отсут-ствию сигнала, а не к возникновению нескольких ложных, что мень-ше влияет на работоспособность системы н облегчает поиск неисправ-ности.

Интерфейсы ММС стандартизируются на национальном и меж-дународном уровнях. Среди многих проектов можно выделить основ-ные, ставшие стандартами де-факто, которые в модернизируемом ви-де (по рекомендациям рабочих групп IEEE и IEC) или в полном со-ответствии с проектами, представленными рабочими группами или фирмами, рассматриваются как международные стандарты.

Стандарт IEC BUSI базируется на стандарте IEEE P-796 (вари-ант системной магистрали интерфейса MBI) и специфицирует: прото-кол, физическую реализацию в соответствии с Р-796, физическую ре-ализацию на основе Европлат с высотой 233,4 мм и 100 мм, глу-биной 160 мм, с разъемом по МЭК 603-2. По сравнению с Р-796 число линий адреса увеличено до 24 и оговорены функции второго разъема.

Проект стандарта VME-bus (проект Р-1014, стандарт IEC 821) разработан на основе 16-разрядного варианта IEEE Р-961 путем до-бавления второго разъема. Интерфейс в основном ориентируется на 16-разрядпые ММС, использующие МП типа МС 680ХХ. Интер-фейс обычно применяется как процессорная шина в ММС, в платах процессоров которых не используется локальная двухвходовая па-мять. Однако в проекте VME не разрешены задачи по обеспечению совместимости модулей 16- и 32-разрядных ММС, а также конфигу-раций ММС с различными разрядностями адреса и вариантами ис-полнения.

Проект стандарта МВП разработан фирмой Intel. В 1983г. фирма распространила его среди изготовителей ММС для содействия и проверке и завершения стандарта. Комитет по МВП института ]ЕЕЕ в проекте Р-1296 на параллельную системную магистраль в 1986 г. уточнил основные положения спецификации, в том числе по использованию двойных Европлат (6U), терминологии и других шин, не рассмотренных в проекте PSB системы МВП, с целью более широкого его распространения среди пользователей, которые заинте-ресованы в процессорно-независимом стандартном интерфейсе для 32-разрядных ММС, ориентированных на промышленные применения в реальном масштабе времени.

Организации по стандартизации интерфейсов СЭВ (секция 2) и СССР в качестве основных стандартов ММС рассматривают сле-дующие: И-41, аналогичный проекту IEC BUSI; И-42, аналогичный проекту Р-1296; интерфейс, аналогичный проекту IEC 821.

Интерфейс И-41 (ОСТ 25969-83) является аналогом IEC BUSI и предназначен для построения сосредоточенных многопроцессор-ных модульных систем обработки данных, микропроцессорных комп-лексов, микроЭВМ, ПЭВМ. Он обеспечивает программный обмен данными одного или нескольких процессоров с памятью и с конт-роллерами ввода-вывода, прямой доступ к памяти (ПДП) н генера-цию прерываний. Интерфейс использует два независимых адресных пространства (памяти и ввода-вывода) и обеспечивает прямую адре-сацию до 16 Мбайт памяти с использованием 24-разрядного адреса, а также до 64 Кбайт портов ввода-вывода (ПВВ) с использованием 16-разрядного адреса. В циклах обращения к памяти и в циклах ввода-вывода возможны 8- и 16-разрядные передачи данных. Задатчики с байтовой организацией используют 16 адресных линий для адресации памяти и 8 - для выборки ПВВ, адресуя 64 Кбайта па-мяти и 256 ПВВ. Интерфейс применяется в микроЭВМ СМ1800, СМ1810, ПЭВМ <Искра 1030>, <Нейрон И9.66> и др.

Интерфейсные системы Multibus фирмы Intel с архитектурой Multibus I (MBI) и Multibus II (МВП) предназначены для построе-ния ММС, в основном использующих МП типов 8080, 8085, 8086, 80286, 80386 (отечественные МП КР580ВМ80, KM182IBM85, KP18IOBM86),

Архитектура MBI содержит пять магистралей: две параллельные Multibus и LBX, многоканального ввода-вывода Multichannel, локаль-ного ввода-вывода SBX и последовательную Bitbus.

Системная магистраль Multibus (IEEE P-796) - одна из наиболее распространенных в мире. Магистраль использует асинхронный про-токол со скоростью до 5 Мслов/с (8- или 16-разрядных) в 24-разряд-ном адресном пространстве и обеспечивает мультипроцессорную ра-боту.

Локальная магистраль LBX является расширением внутренней магистрали МП модулей и используется для подключения к ним до-полнительных модулей памяти. Скорость передач на локальной ма-гистрали выше, чем на системной, так как нет потерь времени на ар-битраж. Скорость 8-разрядных передач-до 9,5 Мбайт/с, 16-разряд-ных-до 19 Мбайт/с.

Магистраль Multichannel освобождает СМ от операций ВВ, по-вышая производительность системы. К магистрали может подклю-чаться до 16 устройств. Она может использоваться также для свя-зи микросистем между собой на расстояние до 15 м. По магистрали могут передаваться 8- или 16-разрядные данные со скоростью до 8 Мбайт/с.

Магистраль SBX (IEEE P-959) позволяет наращивать одноплат-ные ЭВМ дополнительными <накладными> платами, расширяющими возможности машин в отношении аппаратной арифметики, параллельного и последовательного ВВ, графики и т. д. без существенных дополнительных затрат. Она позволяет подстраивать структуру ЭВМ под конкретную задачу пользователя. Скорость передач - до 10 Мбайт/с.

Последовательная магистраль Bitbus обеспечивает распределен-ное подключение до 250 устройств обработки данных ВВ и програм-мируемых периферийных контроллеров к различной среде передач длиной до 30 м (для синхронного режима при скорости 2,4 Мбит/с) is до 1200 м (для режима с самосинхронизацией при скорости 62,5 Кбит/с).

Интерфейс МВП (IEEE P-1296) разработан для высокопроизво-дительных мультипроцессорных систем. Архитектура МВП содержит шесть независимых магистралей: две параллельные, PSB и LBXII, последовательную системную SSB и три магистрали, заимствованные из архитектуры MBI: многоканального ввода-вывода Multichannel, локального ввода-вывода SBX и последовательную Bitbus. Структу-ра каждой магистрали не зависит от типа МП и учитывает требова-ния будущих МП. Одновременное использование магистралей обес-печивает пропускную способность 96 Мбайт/с (PSB - 40 Мбайт/с, LBXII -48 Мбайт/с, Multichannel - 8 Мбайт/с).

Благодаря большой пропускной способности в системе можно ис-пользовать много процессорных модулей без перегрузки магистрали. Поскольку применяемые процессорные модули приобретают все более широкие функциональные возможности, запас по пропускной спо-собности позволяет наиболее эффективно использовать каждый до-бавляемый модуль для повышения производительности системы.

Системная магистраль PSB является высокопроизводительной магистралью общего назначения, которая обеспечивает передачи важнейших данных и межпроцессорные взаимодействия. В ней име-ются средства инициализации и конфигурации системы, арбитража. Она позволяет работать с 32-разрядным адресным пространством памяти, 16-разрядным пространством адресов ВВ, 16-разрядным пространством внутренних соединений и 8-разрядиым пространством сообщений. Разрядность передаваемых данных 8/16/24/32 бита.

Локальная магистраль LBXII обеспечивает эффективное исполь-зование процессором памяти, расположенной на других, печатных платах. Она позволяет обращаться к памяти объемом до 63Мбайт. Ее применение на 60...90 % разгружает системную магистраль. По-скольку магистраль оптимизирована для вычислений, она не произ-водит операций ВВ и передачи сообщений.

Последовательная магистраль SSB позволяет создавать локаль-но распределенные системы из нескольких микросистем или осуществ-лять связь с приборами.

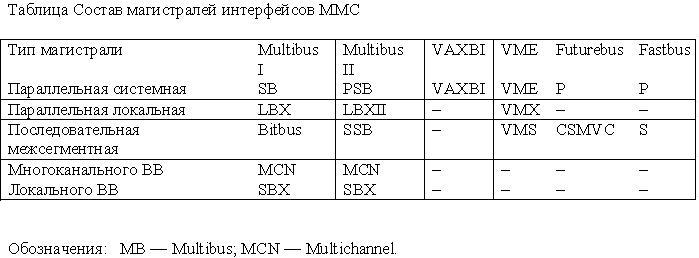

В архитектуре МВП существует четыре адресных пространства. Пространство межсоединений используется для идентификации мо-дулей и конфигурации системы, а также для тестирования и диагно-стики. Пространство памяти используется для доступа к устройст-вам памяти, хранения и выборки данных и программ. Пространство ВВ используется для доступа к ПУ, модулям устройств связи с объ-ектом (УСО), контроллерам системы передачи данных (СПД) и ВЗУ большой емкости. Пространство сообщений используется для межмодульных и межпроцессорных связей при передаче информации о прерываниях и пересылке данных.

Каждое адресное пространство может быть доступно несколь-ким магистралям (табл.). Каждому модулю, соединенному с магистралями.

PSB или LBXII, должен быть присвоен свой адрес или группа адресов в пространстве межсоединений. Идентификатором взаимосвязи является идентификатор места (ИМ) платы, который принимает свое значение при включении питания. На магистрали PSB значение ИМ меняется от 00 до 19. Центральный обслужива-ющий модуль (ЦОМ) всегда имеет ИМ, равный 00. На магистрали LBX1I значение ИМ меняется от 24 до 29. Первичный задатчик всег-да имеет ИМ, равный 24.

Адрес пространства межсоединений состоит из ИМ и последовательных номеров регистров (до 512). Регистры 0 и 1 имеют одну, функцию для всех модулей и являются идентификаторами постав-щика, остальные определяются пользователем Регистры 2 и3 на-пример, могут содержать идентификатор типа модуля, 4 и 5 - лите-ру исполнения, 6 и 7 - нижнюю границу адресного пространства памяти модуля, 8 -число блоков 64К в модуле. Пространства па-мяти и ВВ являются широко используемыми пространствами для работы с памятью и устройствами ВВ.

Пространство сообщений используется дли реализации мультипроцессорных архитектур, требующих межпроцессорного взаимодей-ствия. Модулям, использующим это пространство, назначается адрес пространства сообщений, который используется для распознавания сообщений, направленных модулю. Адрес 0FFH используется как широковещательный адрес, относящийся ко всем модулям.

Одни и те же операции могут выполняться через разные магист-рали. При этом задатчик должен однозначно выбирать магистраль, выставляя определенный локальный адрес внутри модуля, исполни-тель должен распознавать магистраль по адресным и управляющим сигналам, и каждая магистраль должна быть прозрачна для про-граммного обеспечения.

Технология шины VMEbus зародилась в 1979 году как спецификация компании Motorola и в 1987-88 гг. была признана международным стандартом (IEEE 1014, IEC821). Эта магистрально-модульная архитектура выдержала конкуренцию с Multibus, FUTUREbus+ и, как следует из данных на рис. 1, несмотря на почтенный возраст, остается лидером для промышленной автоматизации. По-видимому, успех стандарта VME стал следствием множества факторов.

Интерфейс VME-bus (Versabus Module Europe-bus), разработан-ный на основе документа Versabus (IEEEP-96I), предназначен для построения модульных вычислительных систем (МВС), в основном использующих МП фирмы Motorola типов 6800, 68000, 68020. Интер-фейс содержит три магистрали: две параллельные, VME, VMX, и по-следовательную VMS. Архитектура магистрали VME предусматрива-ет раздельные 8- и 16-разрядные тракты данных и 16- и 24-разрядные тракты адреса в одном соединителе. При использовании второго сое-динителя на плате реализуются 32-разрядные тракты данных и адре-са. В магистрали VME реализована многопроцессорная работа с че-тырьмя линиями арбитража и семью линиями прерывания.

Магистраль VMX использует оставшиеся контакты второго сое-динителя и имеет 32-рязрядпую шину данных и 24-разрядную муль-типлексированную шину адреса. Магистраль VMX обеспечивает рас-ширение локальной шипы процессорного модуля на пять соседних мест объединительной платы, что позволяет процессору обращаться к дополнительной памяти без затрат времени па арбитраж и осво-бождает основную магистраль VME. Магистраль VME предусматри-вает также связь модулей памяти с контроллером ПДП. Имеется вариант магистрали MVMX32, предусматривающий мультиплексиро-ванную 32-рззрядную шину адреса-данных.

Последовательная магистраль VMS с автоматическим арбитра-жем использует две линии для передачи данных и предназначена для обмена короткими и срочными сообщениями в системах с непосред-ственной связью и с гибко связанными процессорами. Магистраль VMS можно использовать для связи как в одном крейте, так и ме-жду процессорами в разных крейтах.

Технология VME позволяет создавать вычислительные системы в очень широком диапазоне производительности, от настольных компьютеров до многопроцессорных супер-ЭВМ, от простых и дешевых промышленных контроллеров до мощнейших многопроцессорных систем управления десятками тысяч аналоговых и цифровых каналов ввода/вывода. Не претендуя на достижение рекордных показателей, VMEbus обеспечивает наилучшее соотношение цена/производительность для системы в целом и предоставляет хорошие возможности для наращивания ресурсов.

Важным фактором стало то, что продвижением и развитием стандарта VME занимается организованная в 1984 году международная ассоциация VITA - VFEA International Trade Association. Ее основные спонсоры - крупнейшие американские компании Motorola и Sun Microsystems. Членами VITA являются около 100 европейских, американских, азиатских производителей совместимой продукции VMEbus: DEC, HP, Force Computer, Microware, IBM и др.

После официального принятия стандарта заботой комитета стало поддержание жизнеспособности VME в соответствии с быстро меняющимися технологическими условиями. Ввод в строй нескольких расширений и новой версии стандарта для 64-разрядной передачи данных VME64 показал, что потенциал шины VME далеко не исчерпан. Новейшие реализации VMEbus обеспечивают пропускную способность 320 Мбайт/с.Архитектура VME выросла вокруг семейства Motorola 68xxx, но сейчас имеются VME-реализации для RISC-процессоров, рабочих станций Sun, DEC, HP, SGI, Intel и клона PowerPC. По данным [3], на сегодня существует 370 различных процессорных плат VME, которые выпускает 61 компания. Из общего числа 39% плат центральных процессоров поддерживают 64-разрядную передачу данных, 61% - 16- и 32-разрядную.

Конструктивно в основу VMEbus положен самый популярный механический стандарт - Евромеханика. Конечная система компонуется из функциональных модулей VME, устанавливаемых в крейты, число которых не ограничено. Крейт представляет собой каркас с объединительной магистралью VME, источником питания и вентиляцией. В каждый крейт можно поместить до 21 модуля VME. Модули соединяются через объединительную плату с нормированным волновым сопротивлением и терминаторами на каждой сигнальной линии. В качестве соединителей используются надежные 96-штырьковые разъемы DIN602-3, причем 8- и 16-разрядные модули имеют один разъем, 32/64-разрядные - два.Сегодня технология VME, кроме основного стандарта VMEbus/VME64, включает несколько расширений.

Технология оперативной замены Live Insertion представляет собой минимальное аппаратное дополнение к стандартным модулям VMEbus, позволяющее беспрепятственно вставлять/вынимать модули из работающей системы. Для реализации горячей замены предложен специальный механизм изоляции модуля от шины.

Широкое распространение получил стандарт измерительных систем VXIbus, который поддерживают более 200 зарубежных фирм, выпускающих свыше 500 типов модулей.

В 1995 году был принят стандарт мезонинных технологий ANSI/VITA 4 на модули IP (Industry Pack).

Для телекоммуникаций предложен стандарт SCSA подшины для обработки цифровой аудио- и видеоинформации в телефонии. VMEbus используется как основная управляющая шина системы, а SCSA P2 - для интерфейса с телефонными цепями.

Работа над спецификацией VME64 уже завершена, хотя отделение VITA по стандартам продолжает уточнять расширения к стандарту VME64, но, по всей вероятности, массовое производство VME-изделий, включающих эти расширения, начнется не раньше 1998-99 г. Сейчас же VME-системы ощущают сильное давление дешевых систем на базе ПК. Однако можно рассчитывать, что после того, как новые расширения VME64 будут освоены на рынке высокопроизводительной аппаратуры, высокая рентабельность VME-систем восстановится. Это подтверждается и тем, что за последний год самые высокие темпы развития в VME-сообществе имели три компании, специализирующиеся на быстрых вычислениях: Mercury, Sky Computers и CSPI.

ПК проектируются для работы в комфортных условиях офиса, и их использование в производственной обстановке зачастую невозможно. С другой стороны, разработчики систем промышленной автоматизации не могут игнорировать продукты, имеющие массовое распространение на рынке и, следовательно, относительно дешевые. Прогресс технологии производства электронных плат сделал выгодным изготовление широкой номенклатуры микросхем В/В в виде кристаллов. Для того чтобы их можно было использовать в промышленных системах, требовалась по крайней мере стандартизация с учетом требований повышенной надежности.

За основу была взята 32/64-разрядная высокопроизводительная шина PCI, локальный интерфейс подсистемы В/В для надплатных расширений активной материнской платы, ставшая стандартом де-факто для современных ПК. Эта шина имеет массу достоинств: она не зависит от типа микропроцессора, может работать с самыми быстрыми из них, имеет большую пропускную способность и аппарат автоконфигурирования устройств В/В. Сейчас PCI активно применяется в VME-компьютерах для подключения периферии.

После доработки, в 1995 году, был выпущен стандарт CompactPCI, основанный на общепринятой технологии создания надежных промышленных модульных систем - пассивной объединительной магистрали. Большое практическое значение имеет тот факт, что любое ПО, работающее на настольных ПК, может быть без изменений перенесено в систему CompactPCI, а программисты, работающие на ПК, но не имеющие дела с аппаратурой, могут быстро скомпоновать систему CompactPCI, установить ОС и сконфигурировать систему в соответствии с реальными потребностями.

CompactPCI стал достойным конкурентом технологии VME. Однако CompactPCI - относительно новый стандарт, и некоторые необходимые функции в нем либо отсутствуют (горячая замена), либо не доведены до кондиций. Кроме того, номенклатура продуктов CompactPCI пока небольшая, особенно в сравнении с рынком VME/ISA-оборудования. Поэтому сейчас следует ориентироваться на связку двух стандартов, используя CompactPCI как недорогую объединительную панель с высокой скоростью передачи данных.

Интерфейс VAXBI (именуемый также Bitbus) предназначен для построения систем на основе процессоров типа VAX фирмы DEC. Интерфейс реализует синхронный протокол, использует распределен-ный арбитраж, 32-разрядную мультиплексированную шину адреса и данных и общее адресное пространство памяти и ВВ (012 Мбайт пространства памяти и 512 Мбайт пространства ВВ).

Данные передаются блоками по 4, 8 или 16 байт. По магистра-ли (в зависимости от физической реализации устройств) могут пе-редаваться 8-, 16- или 32-разрядные данные. Тактовая частота ма-гистрали- 5 МГц. Максимальная скорость передачи 16-бантовых блоков- 13 Мбайт/с, 4-байтовых - 6,6 Мбайт/с.

Интерфейс RESYM (REdused Synchronous Multiprocessor) пред-назначен для построения недорогих мультипроцессорных систем, использующих 32-разрядные МП. Он реализует синхронный прото-кол, используя 8-разрядную мультиплексированную шину адреса-данных и распределенный арбитраж, Благодаря малой длине линий

магистрали, высокой частоте синхроимпульса (от 20 до 40 МГц) и конвейерной передаче сигналов управления его производительность сравнима с производительностью интерфейсов с 32-разрядными ши-нами.

Дальнейшим развитием интерфейса может быть синхронная по-следовательная передача информации с частотой 100 МГц и выше.

Рассмотренные архитектурные решения относятся к локальному (центральный процессор и локальная шина) и региональному (VMEbus) уровню организации систем промышленной автоматизации. В условиях реального производства необходимо еще наладить взаимодействие центрального управляющего блока с пространственно распределенным оборудованием системы автоматизации - датчиками, исполнительными механизмами, передаточными устройствами, приводами и программируемыми контроллерами.

Такую связь можно было бы реализовать, например, с помощью сети Ethernet, но к промышленным сетям предъявляются особые требования по надежности и помехоустойчивости. Для связи с удаленными цифровыми устройствами промышленного назначения принято использовать бит-последовательные промышленные или полевые шины (bit serial Fieldbus). К этой группе относятся несколько европейских (PROFIBUS (DIN 19245), FIP (UTE-C46-6xx), Bitbus (IEEE 1118), CAN (ISO/DIS 11898), Interbus-S (DIN 9258)) и американских (Foundation, HART) конкурирующих стандартов. Ведется разработка общеевропейского стандарта EN 50170, объединяющего PROFIBUS и FIP.

Каковы основные возможности лидера - PROFIBUS? Это открытый стандарт, определяющий обмен информацией с компонентами автоматизации любых разновидностей - ПЛК, ПК, панелями оператора, датчиками и силовыми приводами. Существует три основных варианта PROFIBUS: FMS, DP и ISP.

PROFIBUS-FMS представляет собой решение для задач взаимодействия на цеховом и полевом (field) уровне иерархии промышленных связей: с его помощью организуется обмен между интеллектуальными field-устройствами и контроллерами, а также между контроллерами. Как правило, на этом уровне обмен информацией осуществляется по запросу прикладного процесса и не является циклическим. Поэтому время реакции здесь не очень существенно, гораздо важнее функциональные возможности.

Модель PROFIBUS позволяет определить коммуникационные связи, объединяющие распределенные прикладные процессы в один общий. Та часть прикладного процесса field-устройства, которая отвечает за взаимодействие, называется виртуальным field-устройством (VFD). Все объекты реального устройства, с которыми можно взаимодействовать (переменные, программы, диапазоны данных), называются объектами коммуникации. Отображение функций VFD на реальное устройство обеспечивается в коммуникационной модели PROFIBUS интерфейсом прикладного уровня. Для этого объекты коммуникации PROFIBUS-станции вводятся в ее локальный словарь объектов - OD. Конфигурация OD может определяться и загружаться в устройство либо его производителем, либо разработчиком -- или может формироваться динамически. OD содержит структуру и типы всех объектов, а также их внутренние адреса в устройстве и представление на шине (индекс/имя). Доступ к объектам при функционировании происходит через сервисные функции протокола PROFIBUS-FMS, которые позволяют, например, опросить/установить значения переменных и массивов, запустить/остановить программу.

Что касается двух других вариантов стандарта, то PROFIBUS-DP - это оптимизированная по производительности версия PROFIBUS, предназначенная специально для взаимодействий, критичных по времени. PROFIBUS-ISP - проект взаимодействующих частей, базируется на технологии PROFIBUS и дополняет ее возможностями управления процессами, включая внутреннюю защиту.

Проект стандарта Fastbus разработан многими рабочими груп-пами, включая IEEE (проект Р-960), IEC/TC45 (проект 243). Интер-фейс используется в мощных высокопроизводительных 32-разрядных ММС при экспериментальных исследованиях в области физики вы-соких энергий. Стандарт совершенствуется в технологии физической реализации с целью использования ЭСЛ-уровней для сигналов ма-гистрали.

В стандарте Fastbus была определена локальная информациойная сеть произвольной конфигурации, работающая в логическом протоколе, впервые едином для модулей, крейтов и сети. Скорость передачи информации через магистраль доведена до рекордного на те времена значения 80 Мбайт/сек, для этого длительность фронтов импульсов пришлось уменьшить до 10 нс - в 10 раз короче, чем в системе КАМАК. Создавали систему Fastbus люди академического склада, они не позаботились разработать подстандарт на дешевую подсистему - более медленную и с меньшим числом разрядов, поэтому Fastbus применяется, главным образом, в самых сложных физических экспериментах. На основе международных стандартов Fastbus в России выпущены ГОСТ 34.340-91 и ГОСТ 34.341-93. В первый стандарт добавлено приложение, определяющее малые крейты и модули. Второй ГОСТ содержит алгоритмы для программирования аппаратурных систем Фастбас. В России система Фастбас, увы, безнадежно опоздала.

Проект стандарта Futurebus (проект Р-896) разрабатывался ин-ститутом IEEE с целью создания единого для промышленных систем процессорно-независимого интерфейса для 32-разрядных ММС буду-щего. В проект окончательной редакции (1986 г.) внесены дополне-ния, сблизившие его с интерфейсами Fastbus и PSB МВП по географической адресации, параллельному арбитражу, распределению контактов. Новые технические решения по физической реализации обеспечивают максимальное быстродействие магистрали при нагру-зочной способности ТТЛ-передатчиков (50 мА), имеющих оптронную развязку.

Развитие магистрально-модульных систем завершает разработка с пышным названием Futurebus ("магистраль будущего") по стандарту США 1991 года. В этой системе сделано одно принципиальное добавление, учитывающее особенность многопроцессорных компьютеров. В таких системах каждый микропроцессор имеет в своем распоряжении вспомогательную кэш-память (слово cache в английском языке означает "небольшой склад чего-либо, удобный для частого использования"). Во время выполнения параллельных ветвей программы у одного из процессоров появляется промежуточный результат, необходимый другим процессорам для дальнейшей работы. Этот результат нужно быстро передать в кэш-памяти нуждающихся процессоров. Процедура таких передач как раз и предусмотрена в стандарте Futurebus.